- Randomization

- Random Stability

- String Methods

- Convert hex, int, bin to string

- Convert string to hex, int, bin

- 10 Useful Utilities

SystemVerilog Generate Construct ¶

Overview ¶.

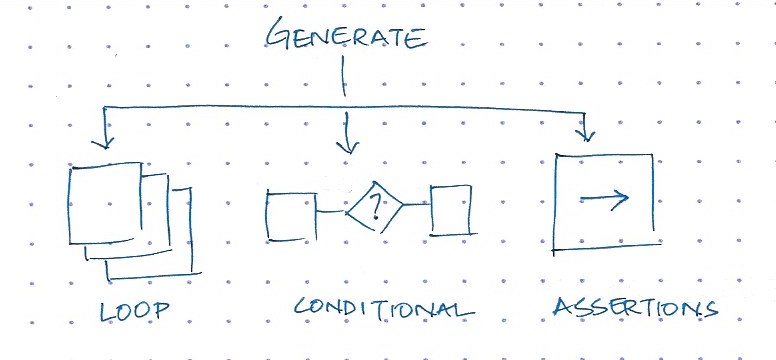

The Generate construct is a very useful tool. You'll commonly see it used for these 3 purposes

- Lazy instantiation of module items using a for-loop

- Changing the structure or design of a module using SystemVerilog Parameters

- Using generate with assertions for Functional and Formal Verification

Before we begin, there's one important thing to understand about the generate construct. Generate blocks are evaluated during elaboration time and the result is determined before the simulation begins. In other words generate statements are NOT a run-time construct. If you think about it for a second, the generate construct is actually creating a circuit and we cannot add or remove hardware circuits on-the-fly, so it does make sense that a generate block is evaluated during elaboration.

Loop Generate Construct ¶

The loop generate construct provides an easy and concise method to create multiple instances of module items such as module instances, assign statements, assertions, interface instances and so on. Think of it as a cloning machine.

In essence it is a special type of for loop with the loop index variable of datatype genvar . Here's an interesting fact about genvar - it is an integer datatype that exists only during elaboration time and disappears at simulation time.

You may also find the testbench for the above example useful!

Check it out here

... and as you would expect, you can nest generate for-loops. Just make sure you use separate genvars for the outer and inner loop and take care while referencing these vars in your nested for-loop. This is a common place where mistakes are made.

Get Notified when a new article is published!

Conditional Generate Construct ¶

The conditional generate construct lets you alter the structure of your design based on Parameter values passed during module instantiation. This is tremendously useful while creating parameterized common RTL blocks for your design.

A simple example -

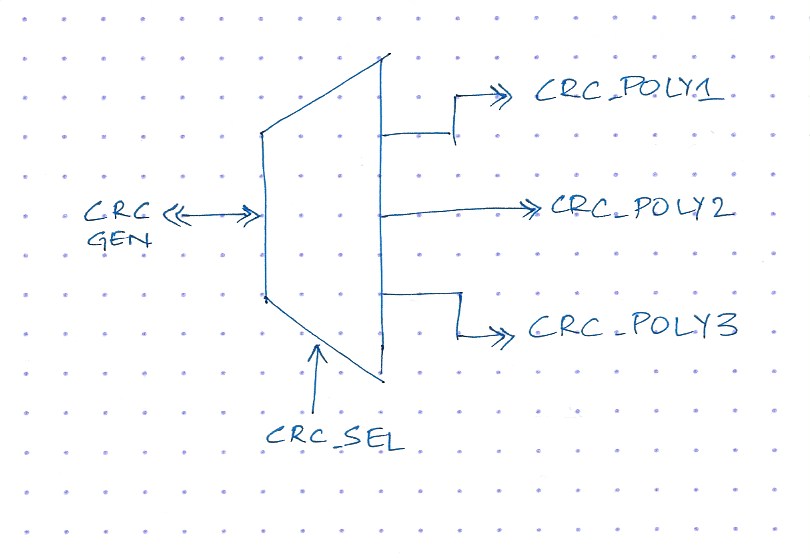

Another example - You've been given the task of creating a common CRC generator block. Other designers in the team should be able to choose between 1 of 3 polynomials for the CRC calculation.

Here is one way to do it - you provide a parameter called CRC_SEL , which is set when this module is instantiated, and this CRC_SEL param selects which CRC function is generated within the module. By using a generate block instead of a simple mux, you save a bunch of gates and flops because the CRC functions that are not required are never instantiated.

The code is explained within comments. An important thing to notice is how the function is called using crc_poly.CRC16_D8() . Read more about it in the code comments.

Certain parts of the code have been omitted to keep the snippet short. Download complete working version of this example

scroll to see more code

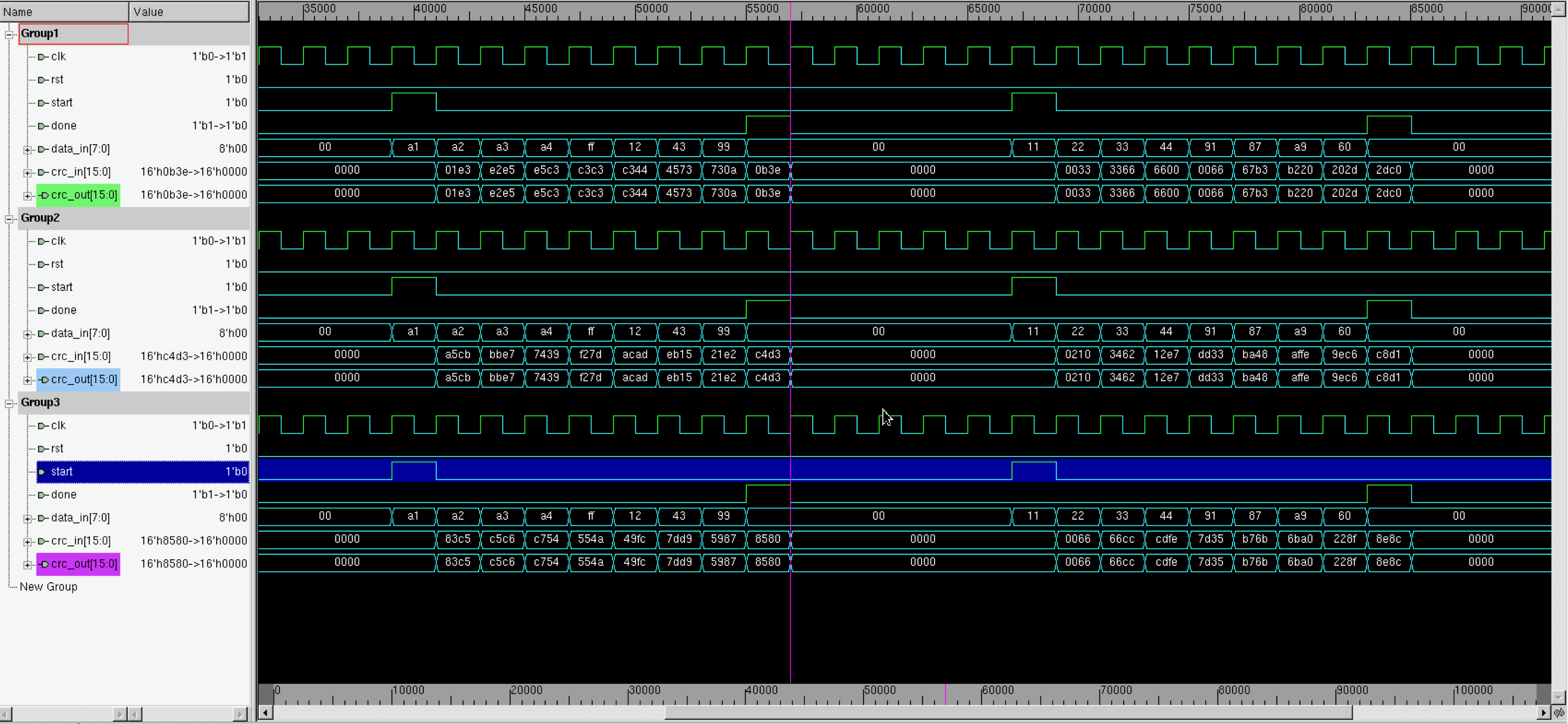

For completion, follow the github link and also take a look at the testbench code for the above crc_gen module, you may find it useful. Here are some waves from the testbench stimulus.

Assertions and Formal Verification ¶

The generate construct is also very useful while writing assertions and this in-turn helps with Formal Verification.

If you have any experience with Formal Verification, then you'll know that Formal tools very quickly run into computational bounds while trying to prove properties. So, it is important to keep your properties short and simple.

For example, if you have an arbiter block with 8 REQquest inputs and 8 ACK outputs, then instead of writing a single assertion to cover all 8 REQ/ACK pairs, it is better to break it down into 8 individual assertions with 1 REQ/ACK pair per assertion.

Here's another example, this is a little more exciting.

Let's say you have a Client - Server system and you have to do Formal Verification on the RTL model of the Client and that of the Server individually. The assertions on the outputs of the Client become assumptions on the input of the Server , and vice-versa. So, instead of writing separate assertions for each of them, this is how you could build your Formal TB.

- Write a common module with all the properties. Define a parameter to tell this "properties module" if the CLIENT_IS_DUT or if SERVER_IS_DUT .

- Bind the properties module to the Client or Server and pass the appropriate Parameter when doing the bind

- Use a recipe of Generate and the Macro constructs to define your properties as assert or assume .

Like this -

The above example was adapted from the book Formal Verification , Erik Seligman, et al. , Chapter 7: Page 194

Hierarchically Accessing Generated Blocks ¶

One thing that trips up people is how to access a module item that are located within a generate block.

A generate block is always given a name. If you don't name it, the compiler will automatically assign a generic name such as genblk01 , genblk02 and you will typically have to dump waves and look at your Visualizer tool to see what names were assigned.

To access a module item within a generate block, you have to hierarchically access it using <generate_blk_name>.<module_item_name> . This is why in example 2.2 we invoked the CRC polynomial function by calling crc_poly.CRC16_D8() (i.e., <generate_blk_name>.<function_name> ).

Here's a nice example from the SystemVerilog LRM 1800-2012 (example 4 section 27.5). Look at how you access the task and module instance defined within the case-generate block.

In a Nutshell ¶

Wrapping things up - this is what we discussed in this article:

- How to use loop generate construct to create multiple instances of module items

- How to use conditional generate construct to change the module's design based on SystemVerilog parameters

- How to use loop and conditional generate constructs with assertions

- How to hierarchically access module items within generate blocks

References ¶

- easics crc tool

- Formal Verification - Erik Seligman, et al.

Questions & Comments ¶

For questions or comments on this article, please use this GitHub Discussions link .

If you would like to be notified when a new article is published, please sign up. If you found this content useful then please consider supporting this site! 🫶

Sign-up for the Newsletter

Every month or so I send out a newsletter with notable technical papers, notifications about new articles and lessons from my experience.

If you found this content useful then please consider supporting this site! 🫶

Verilog Pro

Verilog Generate Configurable RTL Designs

Verilog generate statement is a powerful construct for writing configurable, synthesizable RTL. It can be used to create multiple instantiations of modules and code, or conditionally instantiate blocks of code. However, many Verilog programmers often have questions about how to use Verilog generate effectively. In this article, I will review the usage of three forms of Verilog generate—generate loop, if-generate, and case-generate.

Types of Verilog Generate Constructs

There are two kinds of Verilog generate constructs. Generate loop constructs allow a block of code to be instantiated multiple times, controlled by a variable index. Conditional generate constructs select at most one block of code between multiple blocks. Conditional generate constructs include if-generate and case-generate forms.

Verilog generate constructs are evaluated at elaboration, which occurs after parsing the HDL (and preprocessor), but before simulation begins. Therefore all expressions within generate constructs must be constant expressions, deterministic at elaboration time. For example, generate constructs can be affected by values from parameters, but not by dynamic variables.

A Verilog generate block creates a new scope and a new level of hierarchy, almost like instantiating a module. This sometimes causes confusion when trying to write a hierarchical reference to signals or modules within a generate block, so it is something to keep in mind.

Use of the keywords generate and endgenerate (and begin / end ) is actually optional. If they are used, then they define a generate region . Generate regions can only occur directly within a module, and they cannot nest. For readability, I like to use the generate and endgenerate keywords.

Verilog Generate Loop

The syntax for a generate loop is similar to that of a for loop statement. The loop index variable must first be declared in a genvar declaration before it can be used. The genvar is used as an integer to evaluate the generate loop during elaboration. The genvar declaration can be inside or outside the generate region, and the same loop index variable can be used in multiple generate loops, as long as the loops don’t nest.

Within each instance of the “unrolled” generate loop, an implicit localparam is created with the same name and type as the loop index variable. Its value is the “index” of the particular instance of the “unrolled” loop. This localparam can be referenced from RTL to control the generated code, and even referenced by a hierarchical reference.

Generate block in a Verilog generate loop can be named or unnamed. If it is named, then an array of generate block instances is created. Some tools warn you about unnamed generate loops, so it is good practice to always name them.

The following example shows a gray to binary code converter written using a Verilog generate loop.

Another example from the Verilog-2005 LRM illustrates how each iteration of the Verilog generate loop creates a new scope. Notice wire t1, t2, t3 are declared within the generate loop. Each loop iteration creates a new t1, t2, t3 that do not conflict, and they are used to wire one generated instance of the adder to the next. Also note the naming of the hierarchical reference to reference an instance within the generate loop.

Generate loops can also nest. Only a single generate / endgenerate is needed (or none, since it’s optional) to encompass the nested generate loops. Remember each generate loop creates a new scope. Therefore the hierarchical reference to the inner loop needs to include the label of the outer loop.

Conditional If-Generate

Conditional if-generate selects at most one generate block from a set of alternative generate blocks. Note I say at most , because it may also select none of the blocks. The condition must again be a constant expression during elaboration.

Conditional if-generate may be named or unnamed, and may or may not have begin / end . Either way, it can contain only one item. It also creates a separate scope and level of hierarchy, like a generate loop. Since conditional generate selects at most one block of code, it is legal to name the alternative blocks of code within the single if-generate with the same name . That helps to keep hierarchical reference to the code common regardless of which block of code is selected. Different generate constructs, however, must have different names.

Conditional Case-Generate

Similar to if-generate, case-generate can also be used to conditionally select one block of code from several blocks. Its usage is similar to the basic case statement , and all rules from if-generate also apply to case-generate.

Direct Nesting of Conditional Generate

There is a special case where nested conditional generate blocks that are not surrounded by begin/end can consolidate into a single scope/hierarchy. This avoids creating unnecessary scope/hierarchy within the module to complicate the hierarchical reference. This special case does not apply at all to loop generate.

The example below shows how this special rule can be used to construct complex if-else if conditional generate statements that belong to the same hierarchy.

This generate construct will select at most one of the generate blocks named u1. The hierarchical name of the gate instantiation in that block would be test.u1.g1. When nesting if-generate constructs, the else always belongs to the nearest if construct. Note the careful placement of begin / end within the code Any additional begin / end will violate the direct nesting requirements, and cause an additional hierarchy to be created.

Named vs Unnamed Generate Blocks

It is recommended to always name generate blocks to simplify hierarchical reference. Moreover, various tools often complain about anonymous generate blocks. However, if a generate block is unnamed, the LRM does describe a fixed rule for how tools shall name an anonymous generate block based on the text of the RTL code.

First, each generate construct in a scope is assigned a number, starting from 1 for the generate construct that appears first in the RTL code within that scope, and increases by 1 for each subsequent generate construct in that scope. The number is assigned to both named and unnamed generate constructs. All unnamed generate blocks will then be given the name genblk[n] where [n] is the number assigned to its enclosing generate construct.

It is apparent from the rule that RTL code changes will cause the unnamed generate construct name to change. That in turn makes it difficult to maintain hierarchical references in RTL and scripts. Therefore, it is recommended to always name generate blocks.

Verilog generate constructs are powerful ways to create configurable RTL that can have different behaviours depending on parameterization. Generate loop allows code to be instantiated multiple times, controlled by an index. Conditional generate, if-generate and case-generate, can conditionally instantiate code. The most important recommendation regarding generate constructs is to always name them, which helps simplify hierarchical references and code maintenance.

- 1364-2005 – IEEE Standard for Verilog Hardware Description Language

Share this:

- Click to share on LinkedIn (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on Facebook (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

17 thoughts on “Verilog Generate Configurable RTL Designs”

Great article! I often use for-generate loops but I didn’t know about existing of if- and case-generate conditions 🙂

Thanks for the Posting. I recently saw a “conditional generate” code that I wasn’t aware of. Good to see this detailed explanation.

This is superb. Thanks for this great resource Jason!

Is there a way to use generate blocks for signal declarations? When I check with the systemverilog LRM I see this sentence, “A generate block may not contain port declarations, specify blocks, or specparam declarations.”.

What about internal signal declarations? For instance, if I have two different structs with different fields inside the structs, and I want to choose between the two types for an internal signal declaration type (note not a port) something like the below gives a compile error saying the signal is not declared.

parameter integer unsigned some_parameter = 1;

generate if (some_parameter == 1) begin type_a x; end else if (some_parameter = 0) begin type_b x; end endgenerate

Then at some point below X is referenced.

Thanks in advance!

Hi Sami. That’s an interesting question. I tried something similar to your code and also encountered an error during compilation that the type is unknown. I suspect it’s because generate statement is only resolved during elaboration, but the type needs to already exist during compilation. How I usually handle something like that is if the parameter only affects a field within the struct, I parameterize that field to use the parameter, rather than use generate to select between two structs. Also, you can pass a TYPE as a parameter into a module, and use that TYPE in the struct. That may also achieve what you’re looking for.

Thanks for the quick reply! Yes, what you suggested is the first approached I tried. I have parameters for the width of the fields in the struct. My hope with that approach is if the width parameter is set to 0 then that field should not exist. I wasn’t sure if that would be reality of what would happen. I noticed that in simulations that field shows up with negative index. For example:

parameter FIELD_WIDTH = 0; … logic [FIELD_WIDTH-1:0] x;

This will show up as x[-1:0] in waveforms. What I don’t know is if this is a tool quirk or this will actually synthesize to two bits.

Hi Jason, Great article. Is it possible to change the loop index inside the generate block itself? For example, in a generate block, I have an if statement which generates two instantiations and in the else statement it instantiates one. So I’d like to increment the loop index in the if statement itself. Is it possible? Regards, Kunal

Nice post. Seeing that you are using instances of logic gates. Guess I can instantiate any other module, but what about processes such as “always” or “assign”?

Yes you can also wrap always and assign statements in a generate.

Beautifully written, terse and clear!

Great article but there are several errors,

module for_loop_synthesis (i_Clock); input i_Clock; integer ii=0; reg [3:0] r_Shift_With_For = 4’h1; reg [3:0] r_Shift_Regular = 4’h1;

// Performs a shift left using a for loop always @(posedge i_Clock) begin for(ii=0; ii<3; ii=ii+1) r_Shift_With_For[ii+1] <= r_Shift_With_For[ii]; end

// Performs a shift left using regular statements always @(posedge i_Clock) begin r_Shift_Regular[1] <= r_Shift_Regular[0]; r_Shift_Regular[2] <= r_Shift_Regular[1]; r_Shift_Regular[3] <= r_Shift_Regular[2]; end endmodule

module for_loop_synthesis_tb (); // Testbench reg r_Clock = 1'b0; // Instantiate the Unit Under Test (UUT) for_loop_synthesis UUT (.i_Clock(r_Clock)); always #10 r_Clock = !r_Clock; endmodule

module gray2bin #(parameter SIZE = 8) ( input [SIZE-1:0] gray, output [SIZE-1:0] bin );

generate genvar gi; // generate and endgenerate is optional // generate (optional) for (gi=0; gi<SIZE; gi=gi+1) begin : genbit assign bin[gi] = ^gray[SIZE-1:gi]; end // endgenerate (optional) endgenerate endmodule

module gray2bin_tb(); //Testbench reg [15:0] in,out;

gray2bin #(16) DUT ( .gray(in), .bin(out) );

integer jj=0;

initial begin

for(jj=0;jj<16;jj=jj+1) begin in=jj; #5; end end

i have corrected all of them for you

thank you for making this cheers

Thanks for spotting the typo!

Nice work… Keep going…. Nice page…

Sir gray2bin code is synthesizable yes not and can I implement on the FPGA board

Yes it is certainly synthesizable and can be implemented in FPGA.

Nice article Jason, very helpful for beginners.

in the for loop,what is the meaning of the” gi=0; gi<SIZE; gi=gi+1″ .should gi < size

Leave a Comment Cancel reply

Notify me of follow-up comments by email.

Notify me of new posts by email.

This site uses Akismet to reduce spam. Learn how your comment data is processed .

Verilog generate block

A generate block allows to multiply module instances or perform conditional instantiation of any module. It provides the ability for the design to be built based on Verilog parameters. These statements are particularly convenient when the same operation or module instance needs to be repeated multiple times or if certain code has to be conditionally included based on given Verilog parameters.

A generate block cannot contain port, parameter, specparam declarations or specify blocks. However, other module items and other generate blocks are allowed. All generate instantiations are coded within a module and between the keywords generate and endgenerate .

Generate for loop

- Generate if else

- Generate case

A half adder will be instantiated N times in another top level design module called my_design using a generate for loop construct. The loop variable has to be declared using the keyword genvar which tells the tool that this variable is to be specifically used during elaboration of the generate block.

The testbench parameter is used to control the number of half adder instances in the design. When N is 2, my_design will have two instances of half adder.

a[0] and b[0] gives the output sum[0] and cout[0] while a[1] and b[1] gives the output sum[1] and cout[1] .

See that elaborated RTL does indeed have two half adder instances generated by the generate block.

Generate if

Shown below is an example using an if else inside a generate construct to select between two different multiplexer implementations. The first design uses an assign statement to implement a mux while the second design uses a case statement. A parameter called USE_CASE is defined in the top level design module to select between the two choices.

Testbench instantiates the top level module my_design and sets the parameter USE_CASE to 1 so that it instantiates the design using case statement.

When the parameter USE_CASE is 1, it can be seen from the simulation log that the multiplexer design using case statement is instantiated. And when USE_CASE is zero, the multiplexer design using assign statement is instantiated. This is visible from the display statement that gets printed in the simulation log.

Generate Case

A generate case allows modules, initial and always blocks to be instantiated in another module based on a case expression to select one of the many choices.

Note that because a half adder is instantiated, cin does not have any effect on the outputs sum and cout .

Generate Blocks in Verilog

The generate statement in Verilog is a very useful construct that generates synthesizable code during elaboration time dynamically. The simulator provides an elaborated code of the ‘generate’ block. It provides the below facilities:

- To generate multiple module instances or code repetition.

- Conditionally instantiate a block of code based on the Verilog parameter, however, the parameter is not permitted in the generate statement.

It basically provides control on variables, functions, tasks, and instantiation declarations. A generate block has been written within generate and endgenerate keywords.

Types of generate instantiation

- Verilog gate primitives

- Continuous assignments

- Initial and always blocks

- User-defined primitives

Let’s see what is allowed within the scope of a generate block.

A. Data types

- integer, real

- time, realtime

B. Function and task

Note: Function and task are not allowed within a generate loop, but they are allowed in generate block.

Below module items/declarations are not allowed within the scope of a generate block

- Port declarations like input, output, and inout

- specify blocks

- parameters and local parameters

Methods to write generate statements

Generate loop.

- Generate conditional (includes generate if-else and generate case)

The generate loop is similar to the for loop statement, but it uses genvar keyword as a loop variable.

- The genvar keyword is only used during the evaluation of generate block and does not exist during the simulation of the design. It needs to be used by a generate loop.

- Generate loop provides flexibility to reduce code lines by replacing repetitive statements to a single statement like for loop.

- Similar to a for loop, generate loops also can be nested with different genvar as an index variable.

Example: Using always block inside generate block

This code expands to

Example: Ripple Carry Adder

Generate conditional.

A generate block allows conditionally instantiated using if-else-if construct and case keyword.

Example: generate If-else

In the below example, based on parameter sel full adder or half-adder design is instantiated. By default, parameter sel = 0 means half adder will be instantiated. But from the testbench code, parameter sel = 1 is passed to instantiate full adder. $display can not be used within generate block without initial block, otherwise, it throws an error '$display' is an invalid generate scope construct.

Example: generate case

Similarly, the above example if-else generate block can alternatively use case statement as specified in the below example.

Verilog Tutorials

Generate blocks ¶

V. hunter adams ([email protected]) ¶, introduction ¶.

Generate blocks are a mechanism by which we can generate lots of Verilog. To quote the Sutherland HDL guide, "generate blocks provide control over the creation of many types of module items. A generate block must be defined within a module, and is used to generate code within that module."

Within these generate blocks, you can do things like declare variables, instantiate modules, wire modules together, etc. And furthermore, you can do these things conditionally. Usually, the conditions within a generate block will depend on the value of one or a number of genvars .

A genvar is "an integer variable which must be a positive value. They may only be used within a generate block. Genvar variables only have a value during elaboration, and do not exist during simulation. Genvar variables must be declared within the module where the genvar is used. They may be declared either inside or outside of a generate block." ( Evans and Sutherland HDL guide ).

Because generate blocks are only evaluated at elaboration, any conditionals within a generate block must have arguments which are constant expressions. Recall that the generate blocks are being used to build hardware. It therefore must be the case that all conditionals are evaluatable at compile time. If not, that would suggest we were building hardware at runtime, which doesn't make sense.

Video discussion of the content on this page ¶

Example ¶

Suppose that we wanted to construct a shift register, like the one shown below.

We'll consider two ways of doing this. One using a generate block, and the other without using a generate block. Hopefully, by doing so, the utility of the generate block will be clear.

A shift register without using a generate block ¶

Let us first construct this circuit without using a generate block.

Please note that I have implemented this shift register such that we can replace a section with the generate block. In practice, you may implement this a bit more concisely. This is optimized instead for clarity. The output of this module will be 8 0's, then 8 1's, then 8 0's, etc.

A shift register using a generate block ¶

Instead of building all of the repetitive logic above, we could instead use a generate block. We would do so by creating a separate flip-flop module. This is the logic which we will use the generate block to create many copies of.

We can then use a generate block to instantiate and connect a bunch of copies of this module.

Genvar is a variable used in a generate loop.

Description:

A genvar is a variable used in generate-for loop. It stores positive integer values. It differs from other Verilog variables in that it can be assigned values and changed during compilation and elaboration time.

The genvar must be declared within the module where it is used, but it can be declared either inside or outside of the generate loop.

Writing Reusable Verilog Code using Generate and Parameters

In this blog post we look at the use of verilog parameters and the generate statement to write verilog code which is reusable . This includes examples of a parameterized module , a generate for block , generate if block and generate case block .

As with most programming languages, we should try to make as much of our code as possible reusable.

This allows us to reduce development time for future projects as we can more easily port code from one design to another.

We have two constructs available to us in verilog which can help us to write reusable code - parameters and generate statements.

Both of these constructs allow us to create more generic code which we can easily modify to suit our needs when we instantiate a component.

In the rest of this post, we look at both of these constructs in more detail.

Verilog Parameter

In verilog, parameters are a local form of constant which can be assigned a value when we instantiate a module .

As parameters have a limited scope , we can call the same verilog module multiple times and assign different values to the parameter. This allows us to configure the behaviour of a module on the fly.

As we discussed in the post on verilog modules , we must define an interface to a module when we write one.

We can then use this interface to interconnect a number of different modules within our FPGA design.

As a part of this interface, we can declare parameters as well as the inputs and outputs of the module.

The verilog code snippet below shows the method we use to declare a parameter in a module. When we declare a parameter in a verilog module like this, we call this a parameterized module.

The <parameter_name> field in the verilog code above is used to give an identifier to our parameters.

We use this identifier to call the parameter value within our code, much like with a normal variable.

We can also assign a default value to our parameter using the <default_value> field in the example above.

This is useful as it allows us to instantiate the component without having to specifically assign a value to the parameter.

When we instantiate a module in a verilog design unit, we can assign a value to the parameter using either named association or positional association . This is exactly the same as assigning a signal to an input or output on the module.

However when we write code which uses the verilog 1995 standard, we can only use positional association to assign values to a parameter.

The verilog code snippet below shows the methods we use to assign a value to a parameter when instantiating a module.

Verilog Parameterized Module Example

In order to better understand how we use parameters in verilog, let's consider a basic example.

For this example, let's consider a design which requires two synchronous counters . One of these counters is 8 bits wide whilst the other is 12 bits wide.

To implement this circuit, we could write two different counter components which have different widths. However, this is an inefficient way of coding our circuit.

Instead, we will write a single counter circuit and use a parameter to change the number of bits in the output.

As it is not important to understanding how we use parameterized modules, we will exclude the functional code in this example.

Instead, we will look only at how we declare and instantiate a parameterized module in verilog.

The verilog code snippet below shows how we would write the interface for the parameterized counter module.

In this example we see how we can use a parameter to adjust the size of a signal in verilog.

Rather than using a fixed number to declare the port width, we substitute the parameter value into the port declaration.

This is one of the most common use cases for parameters in verilog.

In the verilog code above, we defined the default value of the BITS parameter as 8.

As a result of this, we only need to assign the parameter a value when we want an output that isn't 8 bits.

The code snippet below shows how we would instantiate this module when we want a 12 bit output.

In this instance, we must over ride the default value of the parameter when we instantiate the verilog module.

Although we use named association in the example above, we can also use positional association to assign values to a parameter in verilog.

The code snippet below shows how we would use positional association to assign the value of 12 to the BITS parameter.

Verilog Generate Statements

We use the generate statement in verilog to either conditionally or iteratively generate blocks of code in our design.

This allows us to selectively include or exclude blocks of code or to create multiple instances of a given code block.

We can only use the generate statement in concurrent verilog code blocks. This means we can't include it within always blocks or initial blocks .

In addition to this, we have to use either an if statement , case statement or a for loop in conjunction with the generate keyword.

We use the if and case generate statements to conditionally generate code whilst the for generate statement iteratively generates code.

We can write any valid verilog code which we require inside generate blocks. This includes always blocks , module instantiations and other generate statements.

The generate block was introduced in the verilog 2001 standard . As a result of this, we can't use this construct in verilog 1995 based designs.

Let's look at the three different types of generate block which we can use in our verilog designs.

Generate For Loop in Verilog

We can use a verilog for loop within a generate block to iteratively create multiple instances of a piece of code.

We typcially use the generate for loop approach to describe hardware which has a regular and repetitive structure.

For example, we may wish to describe a number of RAM modules which we want to control using a single bus .

If we use a generate block rather than manually instantiating all of the modules then we can reduce our code overhead.

The code snippet below shows the general syntax for the generate for block in verilog.

As we can see from this example, the syntax for this approach is virtually identical to the syntax we saw in the post on the verilog for loop .

However, there are two important differences between this approach and the normal for loops.

First of all, we must declare the loop variable using the genvar type.

The second difference is that we declare the loop within a generate block rather than a normal procedural block such as a verilog always block .

This difference is important as it alters the fundamental behaviour of the code.

When we write a generate for block we are actually telling the verilog compiler to create multiple instances of the code block.

In contrast, when we use the normal for loop we are telling the verilog complier to create a single instance of the code block but execute it multiple times.

As an example, let's look a very simple use case where we want to assign data to a 2 bit vector.

The verilog code below shows how we would do this using a generate for and a for loop. In both cases, the functionality of the code is the same but the structure produced is very different.

If we were to unroll the for loop example, we would get the code show below.

In constrast, unrolling the generate for code would result in the code shown below.

From this, we can see how the generate for is fundamentally different to the for loop.

Verilog Generate For Example

To better demonstrate how the verilog generate for statement works, let's consider a basic example.

For this example, we will use an array of 3 RAM modules which are connected to the same bus.

Each of the RAM modules has a write enable port, a 4-bit address input and 4-bit data input. These signals are all connected to the same bus.

In addition, each of the RAMs has a 4-bit data output bus and an enable signal, which are independent for each RAM block.

The circuit diagram shows the circuit we are going to describe.

We need to declare a 3 bit vector which we can then use to connect to the RAM enable ports. We can then connect a different bit to each of the RAM blocks based on the value of the loop variable.

For the data output bus, we could create a 12 bit vector and connect the read data output to different 4-bit slices of the vector.

However, a more elegant solution is to use an array which consists of 3 4-bit vectors. Again, we can then use the loop variable to assign different elements of this array as required.

The verilog code snippet below shows how we would code this circuit using the for generate statement.

After synthesizing this code, we get the circuit shown below.

If Generate Statement in Verilog

We use the generate if block in verilog to conditionally include blocks of verilog code in our design.

We can use the generate if statement when we have code that we only want to use under certain conditions.

One example of this is when we want to include a function in our design specifically for testing.

We can use a generate if statement to make sure that we only include this function with debug builds and not with production builds.

The code snippet below shows the general syntax for the verilog generate if statement.

As we can see from this example, the syntax for this approach is virtually identical to the syntax we saw in the post on the verilog if statement .

However, there is a fundamental difference between these two approaches.

When we write a generate if statement we are actually telling the verilog compiler to create an instance of the code block based on some condition.

This means that only one of the branches is compiled and any other branch is excluded from compilation. As a result of this, only one of the branches can ever be used within our design.

In contrast, when we use the if statement the entire if statement will get compiled and each branch of the statement can be executed.

Each time the if statement code is triggered during simulation, the condition is evaluated to determine which branch to execute.

Verilog Generate If Example

To better demonstrate how the verilog generate if statement works, let's consider a basic example.

For this example, we will write a test function which outputs the value of a 4-bit counter.

As this is a test function, we only need this to be active when we are using a debug build.

When we build a production version of our code, we tie the counter outputs to ground instead.

We will use a parameter to determine when we should build a debug version.

The code snippet below shows the implementation of this example.

When we set the debug_build variable to 1, the synthesizer produces the circuit shown below. In this case, the synthesis tool has produced a four bit counter circuit.

However, when we set the debug_build parameter to 0 then the synthesis tool produces the circuit shown below. In this instance, the synthesis tool has tied all bits of the count signal to ground.

Case Generate in Verilog

We use the generate case statement in verilog to conditionally include blocks of verilog code in our design.

The generate case statement essentially performs the same function as the generate if statement.

This means we can also use the generate case statement when we have code which we only want to include in our design under certain conditions.

For example, we could design a test function which we only want to include in debug builds.

We can then use the generate case statement to determine which version of the code gets built.

The code snippet below shows the general syntax for the generate case statement in verilog.

As we can see from this example, the syntax for this approach is virtually identical to the syntax we saw in the post on the verilog case statement .

When we write a generate case statement we are actually telling the verilog compiler to create an instance of the code block based on a given condition.

In contrast, when we use the case statement the entire case statement will get compiled and each branch of the statement can be executed

Each time the case statement code is triggered during simulation, the condition is evaluated to determine which branch to execute.

Verilog Generate Case Example

To better demonstrate how the verilog generate case statement works, let's consider a basic example.

As the case generate statement performs a similar function to the if generate statement, we will look at the same example again.

This means that we will write a test function which outputs the value of a 4-bit counter.

When we build a production version of our code, we tie the the counter outputs to ground instead.

The verilog code below shows the implementation of this example using the generate case statement.

What is the benefit of using parameterized modules?

We can configure the functionality of the module when we instantiate it. This allows us to make our code easier to reuse.

What do we use generate blocks for in veirlog?

We use them to control the way that our designs are compiled and built. They allow us to conditionally include blocks of code in our design at compilation time.

What is the main difference between a for loop and a generate for block?

The generate for block is evaluated at compile time, meaning only one branch of the code block is ever compiled. All the code of a for loop is compiled and it is evaluated continuously during simulations.

Write a generate for block which instantiates 2 16 bit synchronous counters. The two counters should use the parameterized module example from earlier in this post.

Write a generate for block which instantiates either an 8 bit counter or a 16 bit counter, based on the value of a parameter. The two counters should use the parameterized module example from earlier in this post. You can use either a generate case or a generate if block to write this code.

Using Tasks and Functions in Verilog

In this post we look at how we use tasks and functions in verilog. Collectively, these are known as subprograms and they allow us to write verilog code which is reusable .

As with most programming languages, we should try to make as much of our verilog code as possible reusable. This allows us to reduce development time for future projects as we can more easily port code from one design to another.

Whilst functions should be familiar to anyone with experience in other programming languages, tasks are less common in other languages.

There are two main differences between functions and tasks.

When we write a verilog function, it performs a calculation and returns a single value.

In contrast, a verilog task executes a number of sequential statements but doesn't return a value. Instead, the task can have an unlimited number of outputs

In addition to this, verilog functions execute immediately and can't contain time consuming constructs such as delays, posedge macros or wait statements

A verilog task , on the other hand, can contain time consuming constructs.

We will discuss both of these constructs in depth in the rest of this post. This includes giving examples of how we write and call functions and tasks in verilog.

Verilog Function

In verilog, a function is a subprogram which takes one or more input values, performs some calculation and returns an output value.

We use functions to implement small portions of code which we want to use in multiple places in our design.

By using a function instead of repeating the same code in several places, we make our code more maintainable .

We write the code for functions in the verilog module which we will use to call the function.

The code snippet below shows the general syntax for a function in verilog.

We must give every function a name, as denoted by the <name> field in the above example.

We can either declare the inputs inline with the function declaration or as part of the function body. The method we use to declare the input arguments has no affect on the performance of the function.

However, when we use inline declaration we can also omit the begin and end keywords if we want to.

We use the <arguments> field in the above example to declare the inputs to our function.

We use the <return_type> field to declare which verilog data type the function returns. If we exclude this part of the function declaration, then the function will return a 1 bit value by default.

When we return a value we do it by assigning a value to the name of the function. The code snippet below shows how we would simply return the input to a function. We can also simulate this example on EDA playground .

Rules for Using Functions in Verilog

Although functions are often fairly simple, there are a few basic rules which we must follow when we write a verilog function.

One of the most important rules of a function is that they can't contain any time consuming constructs such as delays, posedge macros or wait statements.

When we want to write a subprogram which consumes time we should use a verilog task instead.

As a result of this, we are also not able to call tasks from within a function. In contrast, we can call another function from within the body of a function.

As functions execute immediately, we can only use blocking assignment in our verilog functions.

When we write functions in verilog, we can declare and use local variables . This means that we can declare variables in the function which can't be accessed outside of the function it is declared in.

In addition to this, we can also access all global variables within a verilog function.

For example, if we declare a function within a module block then all of the variables declared in that module can be accessed and modified by the function.

The table below summarises the rules for using a function in verilog.

Verilog Function Example

To better demonstrate how to use a verilog function, let's consider a basic example.

For this example, we will write a function which takes 2 input arguments and returns the sum of them.

We use verilog integer types for the input arguments and the return types.

We must also make use of the verilog addition operator in order to calculate the sum of the inputs.

The code snippet below shows the implementation of this example function in verilog.

As we have previously discussed, there are two methods we can use to declare verilog functions and both of these are shown in the code below.

We can also simulate this example using EDA playground .

Calling a Function in Verilog

When we want to use a function in another part of our verilog design, we have to call it. The method we use to do this is similar to other programming languages.

When we call a function we pass parameters to the function in the same order as we declared them. This is known as positional association and it means that the order we declare our arguments in is very important.

The code snippet below shows how we would use positional association to call the addition example function .

In the example below, in_a would map to the a argument and in_b would map to b.

Automatic Functions in Verilog

We can also use the verilog automatic keyword to declare a function as reentrant .

However, the automatic keyword was introduced in the verilog 2001 standard meaning that we can't write reentrant functions when working with the verilog 1995 standard.

When we declare a function as reentrant, the variables and arguments within the function are dynamically allocated . In contrast, normal functions use static allocation for internal variables and arguments.

When we we write a normal function, all of the memory which is used to perform the processing of the function is allocated only once. This is process is known as static memory allocation in computer science.

As a result of this, our simulation software must execute the function in it's entirety before it can use the function again.

This also means that the memory the function uses is never deallocated . As a result of this, any values stored in this memory will maintain their value between calls to the function.

In contrast, functions which use the automatic keyword allocate memory whenever the function is called. The memory is then deallocated once the function has finished with it.

This process is known as automatic or dynamic memory allocation in computer science.

As a result of this, our simulation software can execute multiple instances of an automatic function.

We can use the automatic keyword to write recursive functions in verilog. This means we can create functions which call themselves to perform a calculation.

As an example, one common use case for recursive functions is calculating the factorial of a given number.

The code snippet below shows how we would use the automatic keyword to write a recursive function in verilog. We can also simulate this example using EDA playground .

Verilog Task

We use verilog tasks to write small sections of code that we can reuse throughout our design.

Unlike functions, we can use time consuming constructs such as wait, posedge or delays (#) within a task. As a result of this, we can use both blocking and non-blocking assignment in verilog tasks.

Verilog tasks can also have any number of inputs and can also generate any number of outputs. This is in contrast to functions which can only return a single value.

These features mean tasks are best used to implement simple pieces of code which are repeated several times in our design. A good example of this would be driving the pins on a known interface, such as SPI or I2C .

We often write the code for tasks in the verilog module which will be used to call the task.

When we do this, we can also read or write any of the module's global variables inside of the task body.

We can also create global tasks which are shared by all modules in a given file. To do this we simply write the code for the task outside of the module declarations in the file.

The code snippet below shows the general syntax for a task in verilog.

As with functions, there are two ways in which we can declare a task but the performance of both approaches is the same.

We must give every task a name, as denoted by the <name> field above.

When we write tasks in verilog, we can declare and use local variables. This means that we can create variables in the task which can't be accessed outside of the task it is declared in.

In addition to this, we can also access all global variables within a verilog task.

Unlike verilog functions, we can call another task from within a task. We can also make calls to functions from within a task.

Verilog Task Example

Let's consider a simple example to better demonstrate how to write a verilog task.

For this example, we will write a basic task which can be used to generate a pulse. The length of the pulse can be specified when we call the task in our design.

In order to do this, we must declare a single time type input in our task.

We will generate the pulse on a global reg type signal so there is no need to declare any outputs for the task.

The verilog code below shows the implementation of this example using the two different styles of task. We can also simulate this example on EDA playground .

Although this example is quite simple, we can see here how we can use the verilog delay operator (#) in a task. If we attempted to write this code in a function, this would cause an error when we tried to compile it.

We can also see from this example that we don't return a value in the same way as we do with a function.

Instead, we simply assign values to any signals that we have access to either as inputs or as global variables.

We can include and drive as many signals as we want when we write a task in verilog.

Calling a Task in Verilog

As with functions, we must call a task when we want to use it in another part of our verilog design.

The method we use to do this is similar to the method used to call a function.

However, there is one important difference between calling tasks and functions in verilog.

When we call a task in verilog, we can't use it as part of an expression in the same way as we can a function.

We should instead think of task calls as being a short hand way of including a block of code into our design.

As with functions, we use positional association to pass paramaters to the task when we call it.

This simply means that we pass parameters to the task in the same order as we declared them when we wrote the task code.

The code snippet below shows how we would use positional association to call the pulse_generate task which we previously considered.

In this case, the pulse_length input is mapped to the pulse_time variable and the pulse output is mapped to the pulse_out variable.

Automatic Tasks in Verilog

We can also use the automatic keyword with verilog tasks in order to make them reentrant. Again, this keyword was introduced in the verilog 2001 standard meaning it can't be used with verilog 1995 compatible code.

As we talked about previously, using the automatic keyword means that our simulation tool uses dynamic memory allocation.

As with functions, tasks use static memory allocation by default which means that only one instance of a task can be run by the simulation software.

In contrast, tasks which use the automatic keyword allocate memory whenever the task is called. The memory is then freed once the task has finished with it.

Let's consider a basic example to show automatic tasks are used and how they differ from normals task.

For this example, we will use a simple task which increments the value of a local variable by a given amount.

We can then run this a number of times in a simulation tool to see how the local variable behaves using an automatic task and a normal task.

The code below shows how we write a static task to implement this example.

Running this code in the icarus verilog simulation tool results in the following output:

As we can see from this, the value of the local variable i is static and stored in a single memory location.

As a result of this, the value of i is persistent and it maintains it's value between calls to the task.

When we call the task we are incrementing the value which is already stored in the given memory location.

The code snippet below shows the same task except that this time we use the automatic keyword.

From this we can now see how the local variable i is dynamic and is created whenever the task is called. After it has been created, it is then assigned the value of 1.

When the task has finished running, the dynamically allocated memory is freed and the local variable no longer exists.

There are two main differences between tasks and functions, what are they?

A task can have ore than one output but a function can only have one. A function can not consume time but a task can.

What is the difference between an automatic function and a normal function in verilog?

Normal verilog functions use static memory allocation whereas automatic functions use dynamic memory allocation.

Write the code for a function which takes 3 integer inputs and returns the product of them.

Write the code for a task which returns the sum of 2 numbers. However, the result should be delayed by a fixed amount of time before it is returned. The task should take three inputs - one of time type which sets the delay time and the 2 integers that will be summed together. In addition, the task should have one output which is the result of the summation.

An Introduction to Loops in Verilog

In this post, we talk about the different types of loop which we can use in verilog - the for loop , while loop , forever loop and repeat loop .

As we saw in our previous post on sequential statements in verilog , there are a number of statements which we can only use within procedural blocks.

We use these statements to control the way that data is assigned in our verilog design.

The four different types of loop which we can use in verilog are also sequential statements which we use to assign data in our designs.

As a result of this, we can only write loops inside of procedural blocks such as an always block or initial block .

In the rest of this post, we talk about how each of these loops is used in verilog. We then consider a short example for each of these constructs to show how we use them in practise.

Loops in Verilog

We use loops in verilog to execute the same code a number of times.

The most commonly used loop in verilog is the for loop . We use this loop to execute a block of code a fixed number of times.

We can also use the repeat keyword in verilog which performs a similar function to the for loop. However, we generally prefer to use the for loop rather than the repeat keyword in verilog designs.

The other type of loop which we commonly use in verilog is the while loop . We use this loop to execute a part of our code for as long as a given condition is true.

Let's take a closer look at each of these types of loop.

Verilog forever loop

We use the forever loop in verilog to create a block of code which will execute continuously, much like an infinite loop in other programming languages.

This is in contrast to the other types of loop in verilog, such as the for loop and while loop, which only run a fixed number of times.

As we see saw in our previous post on verilog testbenches , one of the most common use cases for the forever loop is generating a clock signal in a verilog test bench.

The forever loop can not be synthesized meaning that we can only use it in our test bench code.

The code snippet below shows the general syntax for the verilog forever loop.

Forever loop example

To better demonstrate how we use the forever loop in practise let's consider an example.

For this example we will generate a clock signal with a frequency of 10MHz which we could use inside of a test bench.

To do this, we firstly assign our signal to an initial value. We then use the forever block to invert the signal at regular intervals.

The code snippet below shows how we would implement this clock example in verilog.

There are two important things to say about this example.

Firstly, note that we use the verilog initial block which is another example of a procedural statement. Any code which we write in an initial block is executed once at the beginning of a simulation.

We almost always use initial blocks rather than always blocks in our testbench code. The reason for this is that they only execute once and we typically only need to run our test once.

The other important thing to note here is the use of the # symbol to model time delays in verilog .

In order for this example to work properly we would need to include the verilog timescale compiler directive in our code.

We use the timescale compiler directive to specify the time unit and resolution of our simulations.

In this instance, we need to set the time units to ns as is shown in the code snippet below.

Verilog repeat loop

We use the repeat loop to execute a given block of verilog code a fixed number of times.

We specify the number of times the code block will execute in the repeat loop declaration.

Although we most commonly use the repeat loop in verilog test benches, we can also use it in sythesizable code.

However, we have to take care when using this construct synthesizable code as we can only use it to describe repetitive structures.

The code snippet below shows the general syntax of the verilog repeat loop

We use the <number> field to determine how many times the repeat loop is executed.

The repeat loop is very similar to the for loop in verilog as they both execute code a fixed number of times.

The main difference between these two types of loop is that the for loop includes a local variable which we can reference inside the loop. The value of this variable is updated on every iteration of the loop.

In contrast, the repeat loop doesn't include this local loop variable. As a result of this, the repeat loop is actually less verbose than the for loop in instances where we don't need this variable.

Repeat Loop Example

The repeat loop is a relatively straight forward construct. However, let's consider a basic example to better demonstrate how it works.

For this example, let's suppose that we have a signal in our design that we want to toggle whenever there is a rising edge on another signal in our design.

The waveform below shows the functionality which we are trying to achieve in this example loop.

However, we only want this toggle action to be effective a total of six times.

We can easily implement this in a repeat block, as shown in the code snippet below.

We can see in this example that we have set the <number> field to 6. As a result of this, the repeat loop will run a total of six times before terminating.

We then use the posedge macro which we talk about in the post on the verilog always block . This macro tells us when a rising edge has occurred on the sig_a signal in our code.

In verilog we use the @ symbol to tell our code to wait for an event to occur.

This simply means that the code will pause at this line and wait for the condition in the brackets to evaluate as true. Once this happens, the code will carry on running.

In this example, we use this operator to block the execution of our repeat loop until a rising edge is detected on the sig_a signal.

Finally, we can use the not verilog bit wise operator (~) to invert the sig_b signal whenever a rising edge has been detected.

The waveform below shows the simulation result of this code, as taken from the icarus verilog simulator and output to the gtkwave wave viewer.

Verilog while Loop

We use the while loop to execute a part of our verilog code for as long as a given condition is true.

The specified condition is evaluated before each iteration of the loop.

As a result of this, all of the code in the block will execute in each valid iteration.

This happens even if the condition changes so that it no longer evaluates to true whilst the code in the block is running.

We can think of the while loop as an if statement that executes repeatedly.

As while loops are generally not synthesizable, we often use them in our testbenches to generate stimulus.

The code snippet below shows the general syntax for a while loop in verilog.

We use the <condition> field in the above construct to determine when the execution of the loop is stopped.

while loop Example

To better demonstrate how we use the while loop in verilog, let's consider a basic example.

For this example, we will create an integer type variable which is increased from 0 to 3. We then print the value of this variable on each iteration of the loop.

Although this is a trivial example, it demonstrates the fundamental principles of the while loop.

The code snippet below shows how we would implement this example. This example can also be simulated on EDA playground .

This example assumes that the iter variable has already been declared and assigned an intial value of 0.

In every iteration of the loop, the second line of the code within the loop body increments the iter variable.

The <condition> field in this example is set so that the loop only executes when the iter variable is less than 4. As a result of this, the iter variable is incremented from 0 to 3 in this loop.

We use the $display system task , which we discussed in a previous post, to print the value of the iter variable on each iteration of the loop. The %0d operator indicates that the variable should be printed as a decimal number.

Verilog For Loop

When writing verilog code, we use the for loop to execute a block of code a fixed number of times.

As with the while loop, the for loop will execute for as long as a given condition is true. The specified condition is evaluated before each iteration of the loop.

We specify this condition as part of the for loop declaration. This condition is used to control the number of times the loop is executed.

Although it is commonly used in testbenches, we can also use the for loop in synthesizable verilog code.

When we use the for loop in synthesizable code, we typically use it to replicate sections of our hardware. One of the most common examples of this is a shift register.

As we previously mentioned, the for loop is very similar to the repeat loop. The main difference is that the for loop uses a local variable which can be used in our loop code.

The code snippet below shows the syntax we use in a verilog for loop.

We use the <initial_condition> field to set the initial value of our loop variable. We must declare the variable that we use in our loop before we can use it in our code.

The <stop_condition> field is the conditional statement which determines how many times the loop runs. The for loop will continue to execute until this field evaluates as false.

We use the <increment> field to determine how the loop variable is updated in every iteration of the loop.

Verilog for loop example

To better demonstrate how we use the for loop in verilog, let's consider a basic example.

For this example, we will write a simple four bit serial shift register using the verilog for loop. Implementing a shift register is actually one of the most common use cases of the for loop.

The shift register can be implemented using a simple verilog array .

We can then assign the input to the shift register to the first element of the array. We then use a for loop to shift the existing contents of the array to the left by one place.

The verilog code snippet below shows how we would implement this shift register using a for loop.

The first thing to notice in this code is that we use a loop variable (i) to reference an element of the array in our loop. We must declare this loop variable before we use it in our code.

As our shift array has four bits, we set the <stop_condition> field so that the loop executes only when the loop variable (i) is less than four.

Finally, we set the <increment> field so that the loop variable is incremented by one in every iteration. This allows us to iterate over every element in the array.

In this example, we make use of non-blocking assignment . The reason for this is that a shift register is an example of a sequential logic circuit.

Therefore, we would have to write this code inside of a clocked verilog always block to properly model a shift register.

Which type of loop do we use to create code which runs continuously?

The forever loop executes continuously.

Which function do we normally use a forever loop to implement in a verilog testbench?

The forever loop is commonly used to implement a clock signal in a verilog testbench

What is the main difference between a for loop and a repeat loop?

The for loop includes a local loop variable which is incremented on every iteration of the loop.

Write a for loop which implements an 8 bit shift register.

Rewrite the previous exercise so that it is implemented using a while loop.

If Statements and Case Statements in Verilog

In this post we talk about two of the most commonly used constructs in verilog - the if statement and the case statement.

We have seen in a previous post how use procedural blocks such as the always block to write verilog code which is executed sequentially .

We can also use a number of statements within procedural blocks which control the way that signals are assigned in our verilog designs. Collectively, these statements are known as sequential statements.

The case statement and the if statement are both examples of sequential statements in verilog.

In the rest of this post, we talk about how both of these statements are used in verilog. We then consider a short example for both of these constructs to show how we use them in practise.

Verilog If Statement

The if statement is a conditional statement which uses boolean conditions to determine which blocks of verilog code to execute.

Whenever a condition evaluates as true, the code branch associated with that condition is executed.

This statement is similar to if statements used in other programming languages such as C.

The verilog code snippet below shows the basic syntax for the if statement.

We can exclude the else and else if branches from the statement if we don't need them.

In fact, we have already seen this in the post on always blocks where we used the posedge macro to detect the rising edge of a clock signal.

We can include as many else if branches as necessary to properly model the underlying circuit.

The if statement uses boolean conditions to determine which lines of code to execute.

In the snippet above, these expressions are given by <expression1> and <expression2>.

These expressions are sequentially evaluated and the code associated with the expression is executed if it evaluates to true.

Only one branch of an if statement will ever execute. This is normally the first expression which evaluates as true.

The only exception to this occurs when none of the expressions are true. In this instance, the code in the else branch will execute.

When we omit the else branch in our if statement code then none of the branches will execute in this case.

The code associated with each branch can include any valid verilog code, including further if statements. This approach is known as nested if statements.

When using this type of code in verilog, we should take care to limit the number of nested statements as it can lead to difficulties in meeting timing.

If Statement Example

We have already seen a practical example of the if statement when modelling flip flops in the post on the verilog always block .

To demonstrate this construct more thoroughly, let's consider an example of a clocked multiplexor.

In this instance, we will use an asynchronously resettable D type flip flop to register the output of a multiplexor .

The circuit diagram below shows the circuit which we will use in this example.

The code snippet below shows how we implement this using a single always block and an if statement.

In this example, we use the first if statement to set the output of the flip flop to 0b whenever reset is active.

When the reset is not active, then the always block has been triggered by the rising edge of the clock. We use the else branch of the first if statement to capture this condition.

We use a second if statement to model the behaviour of the multiplexor circuit. This is an example of a nested if statement in verilog.

When the addr signal is 0b, we assign the output of the flip flop to input a. We use the first branch of the nested if statement to capture this condition.

We then use the else branch of the nested if statement to capture the case when the addr signal is 1b.

It is also possible for us to use an else-if type statement here but the else statement is more succinct. The behaviour is the same in both cases as the signal can only ever be 0b or 1b in a real circuit.

Verilog Case Statement

We use the verilog case statement to select a block of code to execute based on the value of a given signal in our design.

When we write a case statement in verilog we specify an input signal to monitor and evaluate.

The value of this signal is then compared with the values specified in each branch of the case statement.

Once a match is found for the input signal value, the branch associated with that value will execute.

The verilog case statement performs the same function as the switch statement in the C programming language.

The code snippet below shows the general syntax for the case statement in verilog.

It is possible to exclude the default branch of the statement, although this is not advisable. If the default branch is excluded then all valid values of the <variable> must have it's own branch.

As with the if statement, the code associated with each branch can include any valid verilog code.

This includes further sequential statements, such as if or case statements. Again, we should try to limit the number of nested statements as it makes it easier to meet our timing requirements.

Case Statement Example

To better demonstrate the way we use the case statement in verilog, let's consider a basic example.

For this example we will look at a simple four to one multiplexor circuit.

We frequently use the case statement to model large multiplexors in verilog as it produces more readable code than continuous assignment based implementations.

The code snippet below shows how we would implement this circuit using a case statement.

This example shows how simple it is to model a multiplexor using the case statement in verilog. In fact, the case statement provides the most intuitive way of modelling a multiplexor in verilog.

Although this example is quite straight forward, there are a few important points which we should consider in more detail.

The first thing to note in this example is that we use blocking assignment . The reason for this is that we are modelling combinational logic and non-blocking assignment normally leads to flip flops being placed in our design.

Another thing to note here is that we could remove the default keyword from this example. We would then explicitly list the value of addr required to output the value of d instead.

However, we have included the default keyword in this example to demonstrate how it should be used.

Which blocks do we use to write sequential statements in a verilog design?

Sequential statements can only be written within a procedural block such as an always block or initial block.

Which keywords can we exclude from the if statement when they are not required?

We can exclude the else and else if keywords if they are not needed.

How many branches of the if statement can be executed at one time?

A maximum of one branch in an if statement can execute at any time.

When can we exclude the default branch from the case statement?

We can exclude the default branch if all valid values of the input signal are explicitly listed.

Use a case statement to write the code for a six to one multiplexor.

Rewrite the six to one multiplexor from the last exercise so that it uses an if statement.

An introduction to SystemVerilog Data Types

In this post, we talk about the most commonly used data types in SystemVerilog. This includes a discussion of data representation , 2 state vs 4 state types, binary data types and numerical data types .

Although SystemVerilog is considered to be a loosely typed language, we must still declare a data type for every port or signal in our SystemVerilog design.

The type which we specify is used to define the characteristics of our data.

We can use types which interpret data purely as a logical value, for example. We can also use types which interpret our data as if it were a numeric value.

When we assign data to a signal in SystemVerilog, the data is implicitly converted to the correct type in most cases.

As a result, there is often no need necessary to explicitly perform type conversions in verilog.

As SystemVerilog is an extension of verilog, we can use all of the existing verilog data types in our code.

In addition to this, a number of new types were introduced as a part of the SystemVerilog standard.

In this post, we look at both the older verilog data types and the newer SystemVerilog types.

Representing Data in SystemVerilog

When we write SystemVerilog, we often need to represent digital data in our code. We can express this data as either a binary , hexadecimal or octal value.

Unlike in other programming languages, we also need to define the number of bits we have in our data representation.

This is because we are describing hardware circuits when we use SystemVerilog. Therefore, we can create data busses which contain as many bits as we choose.

The code snippet below shows the general syntax we use to represent digital data in SystemVerilog.

2 State vs 4 State Data Types

In verilog, we can assign four different states to the individual bits in our data. These different states are shown in the table below.

We require the high impedance and unknown states to more accurately represent the underlying hardware we are describing in verilog.

However, a number of 2 state data types were introduced as a part of the SystemVerilog extension.

These types are intended to be simpler, more efficient versions of the 4 state types from verilog.

When we use the 2 state data types in SystemVerilog, we can only assign a logical 1 or 0 to the individual bits. Therefore, we should only use these data types in SystemVerilog testbenches.

As they have half as many states, the SystemVerilog 2 state types use half as much memory as the 4 state verilog types.

As a result of this, the 2 state types have faster execution times than their equivalent 4 state type.

The table below shows all of the different types which we can use in SystemVerilog. It also shows which types use the old verilog 4 state encoding and which use 2 state encoding.

Each of these types is described in more depth in the following sections.

Basic SystemVerilog Data Types

Broadly speaking, we can split the SystemVerilog types into two distinct families.

One of these families consists of types which are used to model basic binary data in our code.

We mainly use these types to model simple logic components, connections and busses.

The second family consists of types which we use to model numerical data.

We use these types to model either whole or decimal numbers in our SystemVerilog code.